# Synchronous Buck Controller with 2-Bit VID Inputs to Select Output Voltages

Check for Samples: LGS51215

#### Features

- Wide Input Voltage Range: 4.5V-24V

- Selectable Fixed Frequency 300K/400K/600KHz

- 2-Bit VID Control, Programmable Output Voltage and 0V Output can be Configured

- ±1% System accuracy

- Differential Signal Sampling CSN-CSP

- Configurable Output Voltage Switching Rate

- Output Voltage Indication: Power good Function

- Configurable Load Line Compensation Function

- Fast Loop Dynamic Response

- Internal Power Tube Driven Dead Time Control

- Junction Temperature Range From -40°C to +125°C

#### **Ordering Information**

| Part                      | Package    | Top Mark   |  |  |  |  |

|---------------------------|------------|------------|--|--|--|--|

| LGS51215QT                | QFN 3×3-20 | LGS51215YW |  |  |  |  |

| LGS51215QF                | QFN 4×4-24 | LGS51215YW |  |  |  |  |

| Y: year code W: week code |            |            |  |  |  |  |

#### Description

LGS51215 is a DC-DC synchronous buck controller with adjustable output. LGS51215 has a wide input voltage range of 4.5V to 24V. The output voltage can be dynamically switched by the VID0 and VID1 logic signals. The voltage switching rate can be configured by the softstart Capacitor. FB voltage is configured by a resistor divider network. LGS51215 adopts the current detection control mode, which reduces the complexity of the compensation network. At the same time, it has an ultrafast loop response speed. The inductor current sampling mode is used. Provides a cycle-by-cycle current limiting function with a maximum load of 30A.

Additional features include: soft-start, soft-stop, thermal shutdown, UVLO undervoltage lockout, gate driver undervoltage lockout, and smart current limit shutdown **timer.**

#### Applications

- Notebooks, Desktops & Servers

- I/O Supplies

- Power Bus

- Low-power CPU/GPU power rail

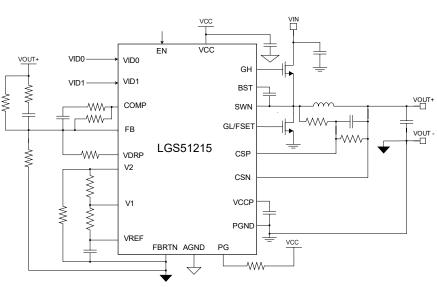

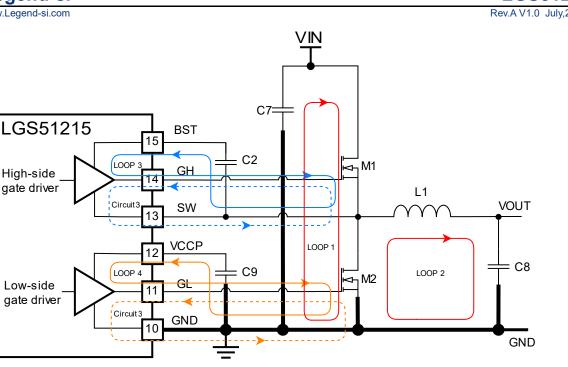

Figure 1.1 Typical Application

Product information is as of the date of publication of the manual. Subject to change without notice.

www.Legend-Si.com

### **Revision History**

Note: Page numbers in previous editions may differ from current edition page numbers.

| Changes from RevA V0.1 Dec.2021 to V0.2 Jan.2022       | Page |

|--------------------------------------------------------|------|

| Updated internal logic diagram and package information | ALL  |

| Changes from RevA V0.2 Jan.2022 to V0.3 Feb.2022       | Page |

| Updated some data and descriptions                     | ALL  |

| Changes from RevA V0.3 Feb.2022 to V0.4 Mar.2022       | Page |

| Updated some data and descriptions                     | ALL  |

| Changes from RevA V0.4 Mar.2022 to V1.0 May.2022       | Page |

| Updated some data and descriptions                     | ALL  |

• The current document is the revised version RevA V1.0, and the relevant parameters of this manual are only recognized for the relevant indicators and descriptions of this version.

Copyright  $\ensuremath{\textcircled{O}}$  2022- present Legend- Si (Nanjing) Semiconductor Co., Ltd.

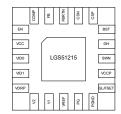

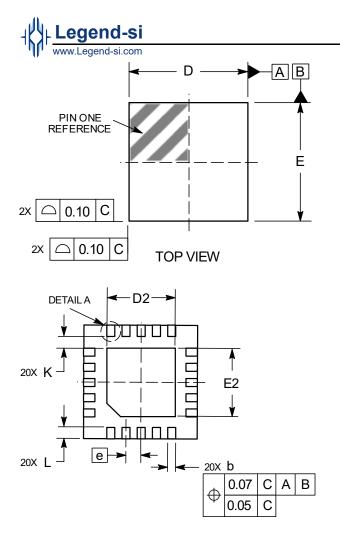

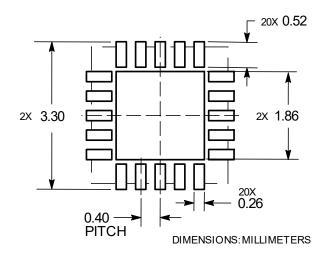

# Package and Pinout Diagram

Figure 3.1 QFN3X3-20L Package

Figure 3.2 Package Reference Top View

### **Pin Function**

Table 4.1 Pin Function Description

| Pin | Name                | Description                                                                                                                                                                                                         |

|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | EN                  | Logic control for enabling the switcher. High level enables the output; Low level disable.                                                                                                                          |

| 2   | VCC                 | Analog control power input. Externally connect at least 2µF ceramic capacitor.                                                                                                                                      |

| 3   | VID0                | Output voltage programming control. Controls output voltage simultaneously with VID1.                                                                                                                               |

| 4   | VID1                | Output voltage programming control. Controls output voltage simultaneously with VID0.                                                                                                                               |

| 5   | VDRP <sup>(1)</sup> | Load line compensation. Putting a suitable resistor between VDRP and FB pin can compensate the output line loss.                                                                                                    |

| 6   | V2                  | Feedback voltage programming. The output voltage can be configured by connecting an appropriate resistor divider in series between VREF, V1, and V2.                                                                |

| 7   | V1                  | Feedback voltage programming. The output voltage can be configured by connecting an appropriate resistor divider in series between VREF, V1, and V2.                                                                |

| 8   | VREF                | reference signal. Configure the output voltage together with V1 and V2, externally connect a ceramic capacitor of no less than 2nF, configure the output voltage soft-start time and output voltage switching rate. |

| 9   | PG                  | Power good indicator of the output voltage. Open-drain output.                                                                                                                                                      |

| 10  | PGND                | Ground reference and high-current return path for the bottom gate driver.                                                                                                                                           |

| 11  | GL/FSET             | Gate driver output of bottom N-channel MOSFET. And it is also used to set up switching frequency by connecting a resistor from this pin to ground.                                                                  |

| 12  | VCCP                | Power supply for MOSFET gate drive                                                                                                                                                                                  |

| 13  | SWN                 | Switch node between the top MOSFET and bottom MOSFET.                                                                                                                                                               |

| 14  | GH                  | Gate driver output of the top N-channel MOSFET.                                                                                                                                                                     |

| 15  | BST                 | Top gate driver input supply, a bootstrap capacitor connection between SWN and this pin.                                                                                                                            |

| 16  | CSP                 | Inductor current differential sense non-inverting input.                                                                                                                                                            |

| 17  | CSN                 | Inductor current differential sense inverting input. It also discharges VOUT during soft-stop.                                                                                                                      |

| 18  | FBRTN               | Feedback Return Input/Output. This pin remotely senses the output voltage.                                                                                                                                          |

| 19  | FB                  | Output voltage feedback.                                                                                                                                                                                            |

| 20  | COMP                | Output of the error amplifier.                                                                                                                                                                                      |

| 21  | AGND                | Analog ground. Bottom thermal pad.                                                                                                                                                                                  |

(1) If this function is not needed, please keep this pin empty.

### Absolute Maximum Ratings (1)

#### Table 5.1

| Parameters                              | MIN  | MAX             | UNIT |

|-----------------------------------------|------|-----------------|------|

| VCC to GND                              | -0.3 | 6               |      |

| SWN to GND                              | -5   | 28              |      |

| BST to SWN、BST to GH、VCCP to PGND       | -0.3 | 6               |      |

| BST to GND                              | -0.3 | 34              | V    |

| FBRTN、PGND to AGND                      | -0.3 | +0.3            |      |

| GL to PGND                              | -0.3 | MIN(VCCP+0.3,6) |      |

| GH to SWN                               | -0.3 | BST+0.3         |      |

| Other Pin to GND                        | -0.3 | 6               |      |

| Storage temperature (T <sub>stg</sub> ) | - 65 | + 150           | °C   |

| Junction Temperature (T <sub>J</sub> )  | - 40 | + 125           | C    |

(1) Temperature range: -40°C - +125°C (unless otherwise specified), if the device operating conditions exceed the above "absolute maximum", it may cause permanent damage to the device. This is only the limit parameter, it is not recommended to operate the device under the limit value or beyond the limit value, the device working under the limit condition for a long time may affect its reliability.

### **Handling Ratings**

#### Table 6.1

|                  |                                                  |                            | VALUE | UNIT |

|------------------|--------------------------------------------------|----------------------------|-------|------|

|                  | Human-body model (HBM)                           | ±2000                      | V     |      |

| V <sub>ESD</sub> | V <sub>ESD</sub> Electrostatic<br>discharge test | Charged-device model (CDM) | ±1000 | V    |

|                  |                                                  | Machine Model (MM)         | ±200  | V    |

#### ESD (electrostatic discharge) sensitive device

Live devices and circuit boards can be electrically charged without being noticed. Although this product has a patented or proprietary protection circuit, the device may be damaged in the event of high energy ESD. Therefore, appropriate ESD preventive measures should be taken to avoid device performance degradation or function loss.

#### **Recommended Operating Conditions** <sup>(1)</sup>

Table 7.1

| Parameter |              | MIN  | MAX | UNIT |

|-----------|--------------|------|-----|------|

| VIN       | VCC/VCCP-GND | 4.5  | 5.5 |      |

|           | EN-GND       | 2    | 5.5 | V    |

|           | VIN-GND      | 4.5  | 24  | , v  |

| VOUT      | Vout         | 0.65 | 2   |      |

| Іоит      | Іоит         | 0    | 28  | А    |

(1) The recommended working conditions are designed to make IC work normally, but do not guarantee the performance of specific parameters. For

details, please refer to the technical specifications in the following article.

# **Technical Specifications**

Unless otherwise specified, VCC=VCCP=5V, VOUT=1V,  $T_A=25^{\circ}C$ . Maximum min applies to  $-40^{\circ}C<T_A=T_J<125^{\circ}C$ . Table 8.1

|                             | Parameter                          | Test Conditions                                                        | MIN  | TYE  | MAX      | UNIT |

|-----------------------------|------------------------------------|------------------------------------------------------------------------|------|------|----------|------|

| Input                       |                                    |                                                                        |      |      |          |      |

| VCC                         | VCC Operation Voltage              |                                                                        | 4.5  | 5    | 5.5      | V    |

| VCCP                        | VCCP Operation Voltage             |                                                                        |      | 5    | 5.5      | V    |

| Vсс_тн                      |                                    | Rising                                                                 | 4.1  | 4.3  | 4.5      | V    |

| Vcc_uvlo                    | VCC Threshold Voltage              | Falling                                                                | 3.5  | 3.9  | 4.1      | V    |

| _<br>Vсср_тн                |                                    | Rising                                                                 | 4.0  | 4.3  | 4.5      | V    |

| VCCP_UVLO                   | VCCP Threshold Voltage             | Falling                                                                | 3.5  | 3.9  | 4.1      | V    |

| lq_vcc                      | VCC Quiescent Current              | VID0=VID1=0V, EN=5V                                                    |      | 300  | 600      | μA   |

| Isd_vcc                     | VCC Shutdown Supply<br>Current     | EN=0V                                                                  |      | 5    |          | μA   |

| I <sub>BST_L</sub>          | BST bias current                   | V <sub>BST</sub> = 34 V, V <sub>SW</sub> = 28 V, T <sub>A</sub> = 25°C |      | 0.1  | 1        | μA   |

| ISD_BST                     | BST Shutdown Supply<br>Current     | EN=0V, BST=5V, SW=0V, T <sub>A</sub> =<br>25°C                         |      |      | 1        | μA   |

| ENABLE                      |                                    |                                                                        |      |      |          |      |

| $V_{\text{EN}_{\text{R}}}$  | Enable voltage threshold           | Rising                                                                 | 1.52 |      |          | V    |

| $V_{\text{EN}_{\text{F}}}$  |                                    | Falling                                                                |      |      | 0.55     | V    |

| I <sub>EN_B</sub>           | EN Input Bias Current              | EN=5V                                                                  |      |      | 1        | μA   |

| $V_{\text{EN}\_\text{MAX}}$ | EN Maximum input voltage           |                                                                        |      | 5.5  | 6        | V    |

| 2-Bits VID                  |                                    |                                                                        |      |      |          |      |

| $V_{\text{VID}\_\text{H}}$  | VID High Threshold<br>Voltage      |                                                                        | 1.52 |      |          | V    |

| Vvid_l                      | VID Low Threshold Voltage          |                                                                        |      |      | 0.55     | V    |

| Ivid_L                      | VID Leakage Current                | VID=0V                                                                 |      |      | 100      | nA   |

| Ivid_L                      | VID Input Bias Current             |                                                                        |      |      | 1        | μA   |

| T <sub>VID_D</sub>          | VID Delay time <sup>(1)</sup>      | Any VID edge to 10% of FB<br>change                                    |      | 200  |          | us   |

| PG Indication               |                                    |                                                                        |      |      |          |      |

| $V_{\text{PG}\_L}$          | Power Good High Leakage<br>Current | I <sub>PG (sink)</sub> =4mA                                            |      | 52   | 80       | mV   |

| IPG_HL                      | PG sets high leakage<br>current    |                                                                        |      |      | 200      | nA   |

| $R_{PG_{L}}$                | PG pull-down conduction resistor   |                                                                        |      | 13   |          | Ω    |

| $T_{PG\_D}{}^{(1)}$         | Power Good Startup Delay           | Measure from SSEND to PG<br>pos edge                                   |      | 3.8  |          | ms   |

| T <sub>PG_H</sub>           | Power Good Propagation             | Delay for power good in                                                |      | 3.4  |          | ms   |

| T <sub>PG_L</sub>           | Delay                              | Delay for power good out                                               |      | 0.35 |          | ms   |

| TMASKING                    | Power Good Masking Time            | Triggered by any VID Change                                            |      | 425  |          | us   |

| Power Stage                 |                                    |                                                                        |      |      | -        |      |

| Fsw_Accuracy                | Switching frequency<br>accuracy    |                                                                        |      |      | ±10      | %    |

|                             |                                    | R <sub>FSET</sub> =2K                                                  |      | 300  |          |      |

| Fsw                         | Switching frequency                | R <sub>FSET</sub> =6K                                                  |      | 400  | <u> </u> | KHZ  |

|                             |                                    | R <sub>FSET</sub> =10K                                                 |      | 600  |          |      |

| VDET                        | Frequency Detection                | Fsw=300K                                                               |      |      | 220      | mV   |

www.Legend-Si.com

| www.Lege               | nd-si.com                                               |                                   |      | F    | Rev.A V1.0 J | uly,2022 |

|------------------------|---------------------------------------------------------|-----------------------------------|------|------|--------------|----------|

|                        | voltage threshold                                       | Fsw=400K                          |      |      | 350          | mV       |

|                        |                                                         | F <sub>SW</sub> =600K             | 450  |      |              | mV       |

| Rsw_L                  | SW pull-down resistance                                 |                                   | 85   |      |              | kΩ       |

| Rghh                   | GH Pull-High Resistance                                 | I <sub>вsт-GH</sub> = 100mA       |      | 0.7  | 1.2          |          |

| Rghl                   | GH Pull-Low Resistance                                  | I <sub>GH-SWN</sub> = 100mA       |      | 0.5  | 0.8          |          |

| Rglh                   | GL Pull-High Resistance                                 | I <sub>PVDD-GL</sub> = 100mA      |      | 0.7  | 1.2          | Ω        |

| Rgll                   | GL Pull-Low Resistance                                  | $I_{GL-PGND} = 100 \text{mA}$     |      | 0.5  | 0.7          |          |

| I <sub>GH_Source</sub> | GH Source Current (1)                                   |                                   |      | 2    |              | Α        |

| $I_{GH}$ SINK          | GH Sink Current <sup>(1)</sup>                          |                                   |      | 2    |              | Α        |

| IGL_Source             | GL Source Current <sup>(1)</sup>                        |                                   |      | 2    |              | Α        |

| Igl_sink               | GL Sink Current (1)                                     |                                   |      | 4    |              | Α        |

| I <sub>DET</sub>       | Frequency detection<br>current                          |                                   |      | 50   |              | μA       |

| TDET                   | Oscillator frequency<br>detection time                  |                                   |      | 200  |              | us       |

|                        |                                                         | GH off to GL on                   |      | 20   |              |          |

| T <sub>SD</sub>        | Dead Time                                               | GL off to GH on                   |      | 20   |              | ns       |

|                        | Minimum MOS conduction                                  |                                   |      |      |              |          |

| Ton_min                | time on high side <sup>(1)</sup>                        |                                   |      | 35   |              | ns       |

| TOFF_MIN               | Minimum MOS turn-off<br>time on low side <sup>(1)</sup> |                                   |      | 250  |              | ns       |

| Internal BST           | •                                                       |                                   |      |      |              |          |

|                        | Schottky diode voltage                                  | I⊧ = 1mA, T <sub>A</sub> = 25°C   |      | 0.3  |              | V        |

| VDIODE                 | drop                                                    | I⊧ = 10mA, T <sub>A</sub> = 25°C  |      | 0.5  |              | V        |

| Error Amplifi          | er                                                      |                                   |      |      | <u> </u>     |          |

| Erro                   | r amplifier dc gain <sup>(1)</sup>                      |                                   | 80   |      |              | dB       |

|                        | fier open-loop bandwidth <sup>(1)</sup>                 |                                   |      | 20   |              | MHz      |

|                        | B bias voltage (1)                                      | Relative to CSN = VID             | -1   |      | 1            | uA       |

|                        | Slew Rate <sup>(1)</sup>                                | COMP pin to GND = 10 pF           |      | 10   |              | V/us     |

| Maxin                  | num output voltage <sup>(1)</sup>                       | 10 mV of overdrive, Isource = 2.0 |      | VCC  |              |          |

|                        | num output voltage <sup>(1)</sup>                       | mA                                |      | 0.2  | 0.3          | V        |

|                        | put Source Current                                      | 10 mV of overdrive, VOUT= 0.3 V   | 2    |      |              | mA       |

|                        | utput Sink Current                                      | 10 mV of overdrive, VOUT=1V       | 2    |      |              | mA       |

| Soft Start             |                                                         |                                   |      |      | <u> </u>     |          |

| ICHG-SS                | VREF soft start charging<br>current                     |                                   |      | 20   |              |          |

| I <sub>CHG-VID</sub>   | VREF increases the<br>charging current                  | VREF 0.65V-2V                     |      | 80   |              | μA       |

| DISC-VID               | VREF decreases the<br>discharge current                 | VREF 2V-0.65V                     |      | 80   |              |          |

| Soft Stop              |                                                         |                                   |      |      |              |          |

| RDISC                  | Output relief resistance (via<br>SCN)                   |                                   |      | 24   |              | Ω        |

| Feedback Vo            | Itage                                                   |                                   |      |      |              |          |

| I <sub>FB</sub>        | FB leakage current                                      |                                   | -500 |      | 500          | nA       |

| VFB                    | FB voltage range                                        |                                   | 0    |      | 2            | V        |

| $V_{FB\_OV}$           | FB overvoltage threshold (1)                            |                                   |      | 2    |              | V        |

| VFB_TH_OV              | V <sub>FB_OV</sub> -VID SET <sup>(2)</sup>              |                                   | 200  | 300  | 400          | mV       |

| Vfb_th_uv              | V <sub>FB_UV</sub> -VID SET <sup>(2)</sup>              | Relative to nominal VID Voltage   | -250 | -200 | -150         | mV       |

|                        | FB Undervoltage                                         |                                   |      |      |              |          |

Copyright © 2022- present Legend- Si (Nanjing) Semiconductor Co., Ltd. LGS51215 – July 2022 *www.Legend-Si.com LGS51215 Product data sheet*

| www.Lege                                   | nd-si.com                              |                                    |       | F    | Rev.A V1.0 | July,2022 |

|--------------------------------------------|----------------------------------------|------------------------------------|-------|------|------------|-----------|

| $V_{FB}$ Accuracy                          | Accuracy of feedback                   |                                    | -1    |      | 1          | %         |

|                                            | voltage                                | <b>T</b> <sub>A</sub> =25℃         | -0.35 |      | 0.35       | %         |

| VREF                                       | Internal reference voltage             |                                    |       | 0.65 |            | V         |

| T <sub>FB_OV</sub>                         | FB Over Voltage Delay                  |                                    |       | 2    |            | μs        |

| Differential C                             | urrent Sense Amplifier                 |                                    |       |      |            |           |

| CSP-CSN common mode input voltage<br>range |                                        | Reference ground is AGND           | -0.2  |      | 2          | V         |

| Differential input voltage range           |                                        |                                    | -30   |      | 30         | mV        |

| Over Current                               | Protection (OCP)                       |                                    |       |      |            |           |

|                                            | OCP Threshold                          | V <sub>SCP</sub> -V <sub>CSN</sub> | 25    | 30   | 35         | mV        |

| LOADLINE                                   |                                        |                                    |       |      |            | •         |

| LOADLINE                                   | Signal amplification factor            | (Vvdrp-Vvref)/(Vcsp-Vcsn)          |       | 6    |            |           |

| Thermal Shut                               | tdown                                  |                                    |       |      |            |           |

| T <sub>SD</sub>                            | Thermal shutdown <sup>(1)</sup>        |                                    |       | 150  |            | °C        |

| T <sub>SD_H</sub>                          | Thermal shutdown delays <sup>(1)</sup> |                                    |       | 25   |            | °C        |

(1) Guaranteed by characterization or design, not production tested

(2) Test results at  $V_{REF}$ =0.65V

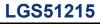

### **Functional Block Diagram**

Figure 9.1 Internal function block diagram

Copyright  $\ensuremath{\textcircled{O}}$  2022- present Legend- Si (Nanjing) Semiconductor Co., Ltd.

### **Typical Application Recommendation**

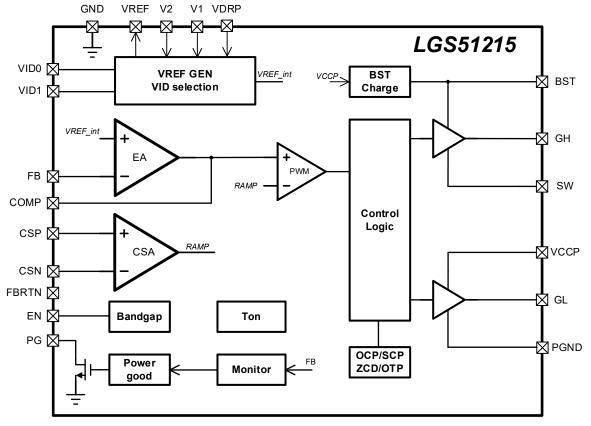

Figure 10.1 Application Circuit Recommendation (VIN=4.5-24V(typical value 12V), VOUT=1V, IO<sub>MAX</sub>=30A, Fsw=300kHz)

| Designator | QTY | Description                             | Manufacturer        | Part Number       |

|------------|-----|-----------------------------------------|---------------------|-------------------|

| MOS        | 1   | 30V Asymmetric Dual N-Channel<br>MOSFET | ON<br>Semiconductor | FDPC5018SG        |

| CIN1-4     | 4   | 10µF, 50V, X5R, 1210, ceramic           | SANYEAR             | C1210X7R106M500NT |

| COUT1-2    | 2   | 220µF, 2.5V, 7343, 9 mill-ohm ESR       | PANASONIC           | 2R5TPE220M9       |

| LRUCK      | 1   | 1μH, ±20%, 1040, 2.3mΩ DCR              | KEMET               | MPCH1040L1R0      |

| LBUCK      |     | 2.2μH, ±20%, 1040, 3.43mΩ DCR           | VISHAY              | IHLP-5050FD-51    |

Table 10.1 LGS51215 Typical external devices are recommended

(1) It is recommended to use X7R or X5R ceramic capacitors for power input and place them as close to IC as possible. See the following description of recommended input capacitors.

(2) For capacitors from BST to SW and VCCP to GND, please select ceramic capacitors with voltage resistance higher than 10V and place them as close to IC pins as possible.

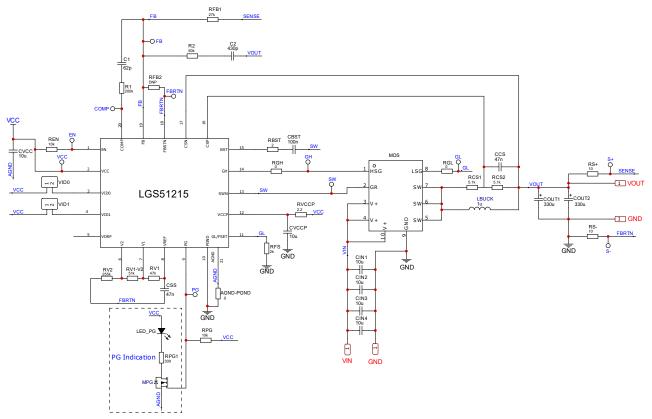

# **Typical Characteristics**

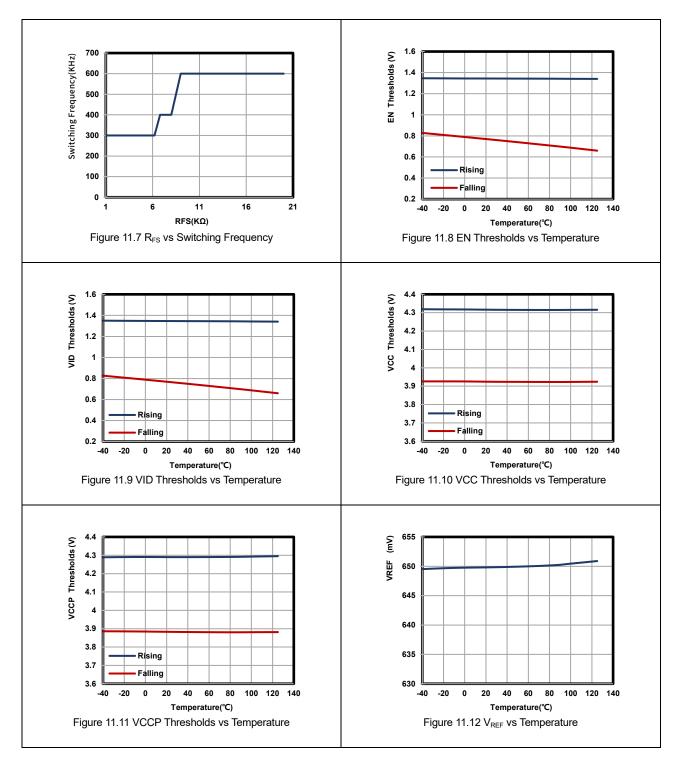

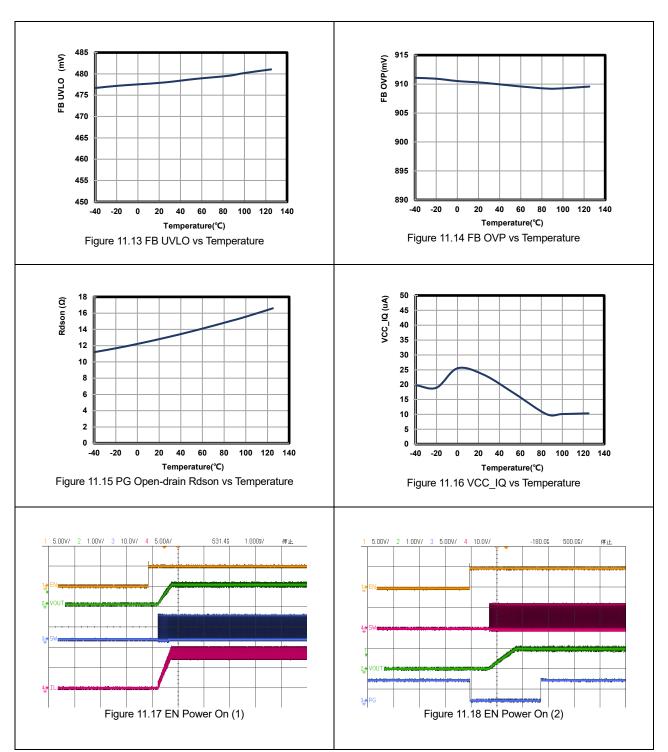

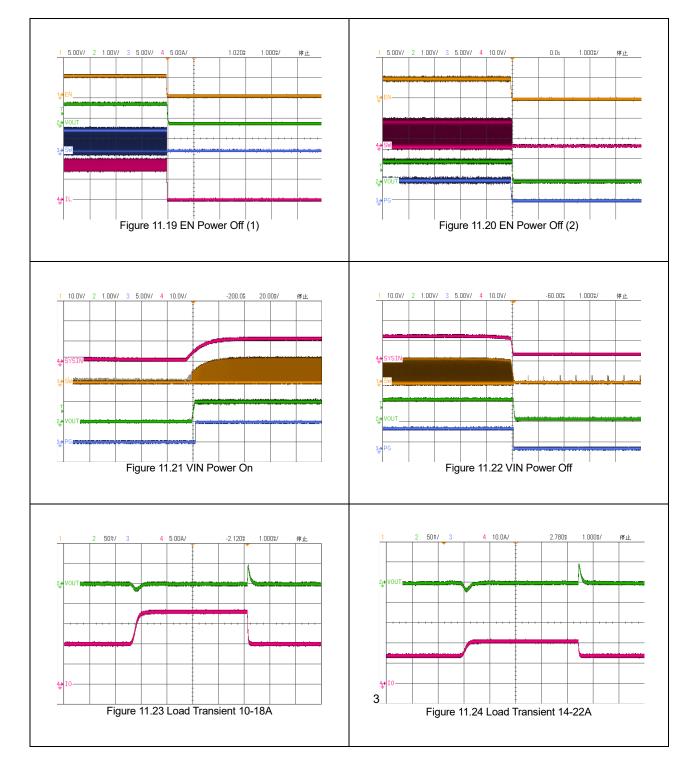

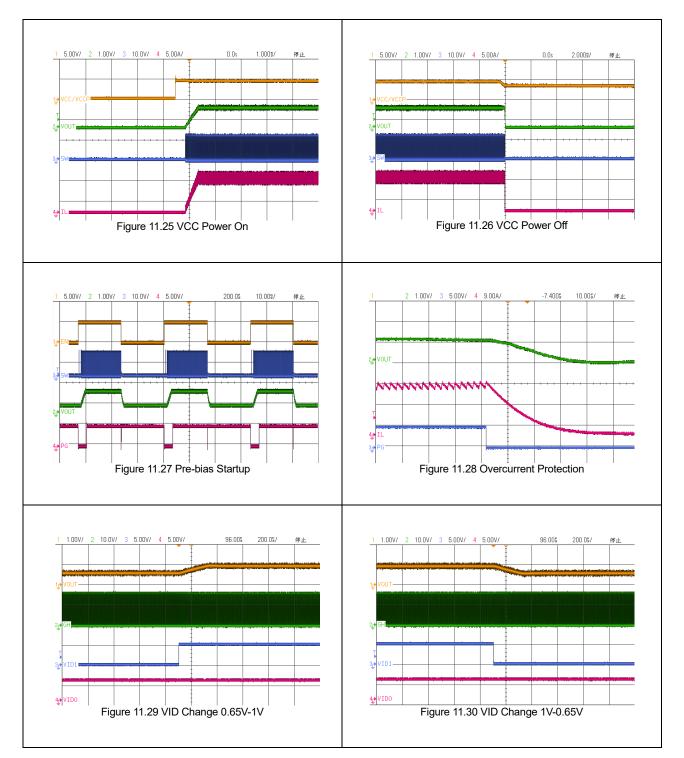

Unless otherwise specified, VIN=12V, VOUT=1V,  $T_A$ =25°C

10

# **Application Information**

#### Overview

LGS51215 synchronous buck controller can operate in the 4.5V to 24V input voltage (VIN) range, providing a natural transition between PFM and CCM, maintaining high efficiency and stability under light load while supporting fast transient response. LGS51215 provides the control functions and protection circuits necessary for a general-purpose controller to meet a wide range of application requirements. LGS51215 supports the output voltage setting function and has a 2-bit VID control mode, which can dynamically change the output voltage of four gears (including 0V) and its switching rate. LGS51215 requires an external 5V voltage source to power and control the internal circuit. The under-voltage locking (UVLO) function protects the internal circuit from low input voltages. LGS51215 can be configured with external resistors to switch frequencies around the 300KHz,400KHz, and 600KHz three-step frequency ranges. LGS51215 provides an upper and lower power tube drive circuit with adaptive dead time, changeable soft start time and extremely low turn-off current, as well as over current protection, good output status monitoring, over voltage protection, under voltage protection, built-in output discharge circuit and thermal turn-off.

#### **Reference Voltage Programming**

LGS51215 provides 2-bit VID control, with four VREF reference voltages (relative to FBRTN) selected by changing the VID state. The design will allow the output voltage to be as low as 0.65V (the internal reference voltage value). When VID0 and VID1 are both low, LGS51215 will turn off GH and GL (the upper and lower power tube drive function). The output voltage will decay gradually to 0V through load consumption.

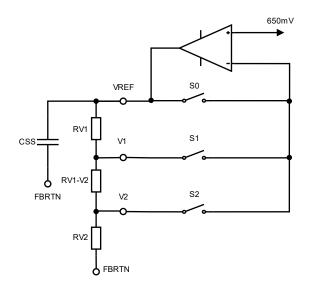

The VID truth tables for each part are listed below.

| VID State |      | Results |                   |         |

|-----------|------|---------|-------------------|---------|

| VID1      | VID0 | Close   | VREF(V)           | VOUT(V) |

| 0         | 0    | /       | 0                 | 0       |

| 0         | 1    | S0      | V <sub>REF0</sub> | VOUT1   |

| 1         | 0    | S1      | $V_{REF1}$        | VOUT2   |

| 1         | 1    | S2      | V <sub>REF2</sub> | VOUT3   |

Table 12.1 VID Truth Table

LGS51215 Rev.A V1.0 July,2022

Figure 12.1 External Reference Voltage Setting

As the picture above shows, When VREF≠0, VREF can be calculated based on the following equations:

$$V_{REF0} = V_{REF-IN} = 650 \text{mV}$$

$$V_{REF1} = V_{REF0} \cdot \left(1 + \frac{R_{V1}}{R_{V1-V2} + R_{V2}}\right)$$

$$V_{REF2} = V_{REF0} \cdot \left(1 + \frac{R_{V1} + R_{V1-V2}}{R_{V2}}\right)$$

Note:  $V_{REF2} > V_{REF1} > V_{REF0}$ . To ensure system stability, keep the total resistance from VREF to FBRTN greater than 100K.

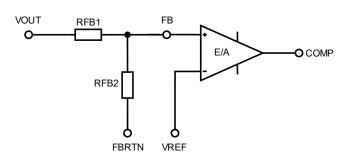

#### **Output Voltage VOUT Setting**

Adding a resistor RFB2 from the FB pin to the FBRTN to form a feedback voltage divider with the resistor RFB1 can be used to increase the output voltage. If the resistor RFB2 is left vacant, the output voltage VOUT will be equal to the voltage of FB. The design keeps the output voltage setting entirely dependent on user requirements, making the LGS51215 more flexible to use.

As shown in Figure 12.2, output voltage can be calculated based on the following equations:

$$VOUT1 = V_{REF0} \cdot \left(1 + \frac{R_{FB1}}{R_{FB2}}\right)$$

$$VOUT2 = V_{REF1} \cdot \left(1 + \frac{R_{FB1}}{R_{FB2}}\right)$$

$$VOUT3 = V_{REF2} \cdot \left(1 + \frac{R_{FB1}}{R_{FB2}}\right)$$

Figure 12.2 Feedback voltage divider

#### **Differential Sensing of Output Voltage**

LGS51215 output voltage is sensed between the FB and FBRTN pins. FB should be connected through a resistor to the positive regulation point. FBRTN should be connected directly to the negative remote sensing point. The LGS51215 combines differential sensing with a high accuracy VID DAC, referenced by a precision band gap source and a low offset error amplifier, to provide accurate output voltage.

#### External Soft-Start Setting and VID Change Slew Rate

To limit the start-up inrush current, a capacitor can be connected from VREF pin to ground to ramp up reference voltage slowly. During this period, the set amplifier output 20  $\mu$ A current to charge capacitor C<sub>SS</sub>. When the VREF voltage is less than the set value, the VREF voltage value follows the soft starting voltage, and will no longer rise when the VREF voltage reaches the set value. In this process, the soft starting voltage continues to rise until the capacitor is charged.

The output current of the set amplifier will change to  $+83\mu$ A/ $-80\mu$ A after soft start period. So during voltage steps due to VID bit change, the slew rate of output voltage. To ensure the stability of the loop operation, please use a high tolerance type MLCC, such as X7R.

#### **Adaptive Gate Driver**

In a synchronous buck converter, a certain dead time is required between the low side drive signal and high side drive signal to avoid shoot through. During the dead time, the body diode of the low side FET free-wheels the current. The body diode has much higher voltage drop than that of the MOSFET, which reduces the efficiency significantly. The longer the body diode conducts, the lower the efficiency. LGS51215 implements adaptive dead time control to minimize the dead time, as well as preventing shoot through from happening.

#### Soft Stop

LGS51215 has Soft Stop discharge mode. a fault (UVP, OVP, OCP, TSD) or disable (EN) causes the output to be discharged through an internal 24-ohm transistor inside of the CSN Pin. The time constant of soft-stop is a function of output capacitance and the resistance of the discharge transistor.

#### Switching Frequency and detection

LGS51215 switch frequency range is set by the resistor  $R_{FS}$  on the GL/FSET pins. After LGS51215 is enabled, the detection switch frequency is set before soft startup. The GL/FSET pin provides 50µA detection current  $I_{FDECT}$ . After 200µs detection time, the voltage of GL/FSET pin is measured to determine the frequency detection threshold. It should be noted that  $I_{FDECT}$  takes longer to charge the GL/FSET pins when the gate capacitance of the low-side MOSFET exceeds 10nF, so users should consider the voltage rise time of GL/FSET during use to ensure that the detection process is completed within 200µs. You can directly use the MOSFET listed in the recommended list of LGS51215 peripherals to ensure the normal use of the chip.

Resistor selection for frequency configuration, please refer to the following table:

| Value Of R <sub>FS</sub> | 2K | 6K | 10K |

|--------------------------|----|----|-----|

|                          |    |    |     |

Fsw 300KHz 400KHz 600KHz

LGS51215 Rev.A V1.0 July.2022

#### **Power Save Mode**

If the load current decreases, LGS51215 will enter power save mode operation. During this mode, the converter skips switching and operates with reduced frequency, which minimizes the quiescent current and maintains high efficiency. The Skip Comparator manages and switches CCM and PFM by comparing the built-in I<sub>SKIP</sub> and I<sub>REF</sub>. When the current demand is lower than I<sub>SKIP</sub>, the comparator controls the suspension of switching. When the current demand increases (VOUT drops), the comparator controls the activation of the current loop into CCM mode, making VOUT rise, at which time the I<sub>REF</sub> will drop, when the I<sub>REF</sub> is lower than I<sub>SKIP</sub>, the switching power tube again suspends switching.

The output voltage ripple in this mode is larger than that in CCM mode because the output voltage drops and recovers irregularly.

#### EN——IC Enabled

The EN voltage controls the startup and shutdown of LGS51215. When the EN voltage is less than  $V_{EN_OUT}$ , the chip remains in low-power standby state. When the voltage at the EN pin is higher than  $V_{EN_OUT}$ , the IC enters soft start mode. During IC shutdown, when EN pin voltage drops to  $V_{EN_OUT}$  -  $V_{EN_HYST}$ , LGS51215 regulator stops working and re-enters standby.

During the test, EN pin can be connected to the VCC through a  $10K\Omega$  resistor, which can be kept on when the VCC is powered on. In actual applications, users can flexibly enable EN based on the application environment.

Note: EN pin has a maximum voltage withstand of 6V and a rated operating voltage of 5V.

#### **Under Voltage Lockout**

There is under-voltage lockout protection for VCC in LGS51215, which has a typical trip threshold voltage 4.3V and trip hysteresis 400 mV. If UVLO is triggered, the device resets and waits for the voltage to rise up over the threshold voltage and restart the part. This protection does not trigger a fault timer to put the chip into the Shutdown state.

#### **Over Voltage Protection and Under Voltage Protection**

When FB voltage is 300 mV (typical) above VREF voltage for over 2 µs blanking time, an OV fault is set. At that moment, the top gate driver is turned off and the bottom gate driver is turned on trying to discharge the output. The bottom gate driver will be turned off when V<sub>FB</sub> drops below under voltage threshold. EN resets or power recycle the device can exit the fault.

The under-voltage limit is 300 mV (typical) below VREF voltage. If  $V_{FB}$  is below this threshold over 3.3 µs, an UV fault is set and the device is latched off such that both top and bottom gate drives are off. EN resets or power recycle the device can exit the fault.

Note: UVP is delayed for soft start after EN goes high. UVP is disabled during VID changes and when VOUT = 0V.

#### **Power Good Monitor**

LGS51215 provides window comparator to monitor the FB voltage. The PG pin is open drain 5-mA pull down output that needs to be connected to the VCC using a pull-up resistor. During startup, PG stays low until the feedback voltage is within the specified range for about 3.3 ms.

(1) The power–good circuit is masked during any VID change. The duration of the PG mask is set to approximately 425µs by an internal timer. (2) PG pin cannot be pulled to a voltage higher than VCC pin voltage.

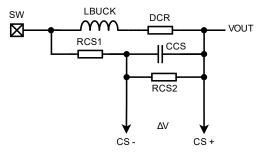

### **Over Current Protection (OCP)**

LGS51215 continuously monitors the current flowing through the inductor through differential current detection. The current limiting threshold  $\Delta V_{TH}$  is 30mV. When the inductor current exceeds the current limiting threshold, the high-side power tube driver (GH) will be turned off periodically.

During the operation of the module, the inductance DCR may be deviated due to the influence of temperature drift. An NTC resistor can be added at RCS2 to compensate for temperature.

Figure 12.3 Inductive DCR current detection circuit

As shown, the inductance current limit can be configured by resistors RCS1, RCS2 and the DCR of the inductor:

$$I_{LIM} = \frac{\Delta V}{DCR} \cdot (1 + \frac{RCS1}{RCS2})$$

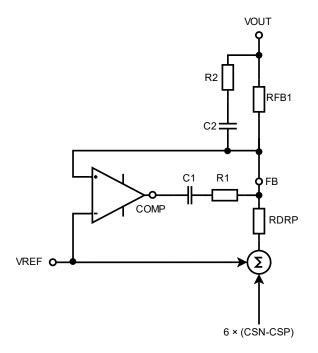

#### Loadline

LGS51215 allows user to program loadline via the VDRP pin. As illustrated in Figure 12.4, LGS51215 outputs a differential signal between VDRP and VREF pins, with its amplitude six times as that of differential signal across CSP and CSN pins. Consequently, user can program a loadline with a resistor, RDRP, between VDRP pin and FB pin, as shown in the following equation:

$$Loadline = 6\Delta V \cdot \frac{RFB1}{RDRP} + VREF$$

If this feature is not required, keep the VDRP pins empty.

Figure 12.4 Load line Circuit

#### **Pre-Bias Startup**

Copyright © 2022- present Legend- Si (Nanjing) Semiconductor Co., Ltd. LGS51215 – July 2022

In some applications, the controller will be required to start switching when its output capacitors are charged anywhere from slightly above 0 V to just below the regulation voltage. This situation occurs for a number of reasons: the converter's output capacitors may have residual charge on them or the converter's output may be held up by a low current standby power supply. LGS51215 supports pre-bias start up. When the load is started with pressure, the output voltage can be monotonously increased and the back current can be avoided.

#### **Thermal Shutdown**

When the junction temperature rises above 150°C, Thermal Shutdown is activated and the system pulls the COMP pin voltage to GND to Shutdown the upper and lower MOSFET. When the junction temperature drops below 130°C, LGS51215 automatically restarts using the soft start function.

The guaranteed operating junction temperature range of the device is  $-40^{\circ}$ C to  $+125^{\circ}$ C, high junction temperature will reduce the working life, when the junction temperature is higher than  $125^{\circ}$ C for a long time, the device life will be shortened. Please note that the maximum ambient temperature consistent with these specifications depends on the specific operating conditions as well as the PCB layout, package thermal rating, and other environmental factors.

Junction temperature ( $T_J$ , unit: °C) is calculated according to the ambient temperature ( $T_A$ , unit: °C) and power ( $P_D$ , unit: W). The calculation formula is as follows:

$$T_J = T_A + \left( P_D \times \theta_{JA} \right)$$

Note:  $\theta_{JA}$  (unit: °C/W) is thermal resistance of packaging.

# PCB Layout and Cabling Guide

Proper PCB layout is critical for the high current, fast switching circuit (with high current and high voltage slew rate) module where LGS51215 controller resides to ensure proper operation and stable output of the buck module. Poor layout can affect the performance of LGS51215, resulting in current sampling deviation, electromagnetic interference, poor electromagnetic compatibility and voltage loss, which in turn affects the stability of use.

Figure 13.1 Power circuit

#### **Power Stage Layout**

VIN input capacitance, output capacitance, and high and low side MOSFET are the power-level parts of the BUCK topology and are typically placed on top of the PCB to maximize convection heat dissipation. Small-signal components can be placed on the back, and at least one internal electrical layer directly connected to GND is added between the top and bottom layers to shield and isolate small signals and noise.

- Loop 1 is the main switching loop circuit of the power stage. The topology of the buck converter determines that a particularly high di/dt current flows through it. Therefore, the loop area of this part must be minimized to minimize parasitic inductance, and the input capacitance of VIN must be kept as close as possible to the drain of the high-side MOSFET. Loop 2 is a loop from the low-side MOSFET through the GND terminal of the inductor and the output capacitor back to the source of the low-side MOSFET. Connect the source of the low-side MOSFET and the negative terminal of the output capacitor as close to GND as possible. Although the current flowing through the inductor and the VOUT output capacitor will be limited by the inductor, the area of Loop 2 should also be designed to be as small as possible.

- The SW pin serves as the switch node of the BUCK module, connecting the source pole of the high side MOSFET, the drain pole of the low side MOSFET, and the high voltage side of the inductor. The design area of the SW pin as an interference source on the PCB should not be too large. This part of the design can be considered according to the layout provided by the MOSFET manufacturer. The high-frequency ringing generated by the resonant loop consisting of the output capacitor and the parasitic inductor generated by the power tube is directly reflected on the SW node

and the peak voltage of the ringing, if not controlled, may exceed the value of the input voltage. To ensure that the peak value of the ringing does not exceed the absolute maximum voltage value of the SW pin, a resistor with a low resistance value (generally  $1-3\Omega$ ) can be added to the driver or a buffer consisting of resistors and capacitors can be connected in series between the SW node and GND to reduce the peak value of the ringing.

#### **Gate Drive Layout**

#### Rev.A V1.0 July,2022

LGS51215's high and low side gate drives include short control delays and adaptive dead zone times, and are capable of responding quickly to rapid ups and downs of high currents, which can cause unacceptable ringing if the PCB is poorly designed. The key to optimize the grid drive is to reduce the parasitic inductance of the circuit, including the series resonant inductance and common source inductance of the grid.

- Loop 3 is the driving circuit of the high-side MOSFET. When the high-side MOSFET is on, the high current flows from the bootstrap capacitor of the BST pin (C2 in Figure 13.1) through the gate drive of the high-side MOSFET, and returns to the negative electrode of capacitor C2 through the SW node. On the contrary, when the high-side MOSFET is closed in loop 3 (the dotted line loop in Figure 13.1 is the same as loop 3), the high current flows from the gate of the high-side MOSFET through SW to return to the source of the high-side MOSFET. Loop 4 is the low side MOSFET drive loop. When the low side MOSFET is on, the large current flows from the capacitor (C9 in Figure 13.1) of VCCP pin to the ground through the gate drive of the low side MOSFET and returns to the negative pole of capacitor C9 via GND. On the contrary, when the low side MOSFET is closed in loop 4 (the dotted line loop with the same color as loop 4 in Figure 13.1), the large current flows from the gate of the low side MOSFET through GND back to the source of the low side MOSFET.

- The gate path from gate driver GH、 GL to high and low side MOSFET should be as short as possible to reduce series parasitic inductance, and use 25mil or wider wiring as far as possible.

- Capacitor C2 should be close to BST and SW pins to minimize loop area of high-side MOSFET drive; The capacitor C9 should be close to the VCCP and GND pins to minimize the loop area of the low-side MOSFET drive.

- Add a resistance of 2Ω-10Ω next to the capacitor C2 of loop 3 to slow down the opening speed of the high side MOSFET, thus reducing the peak ringing value of the SW node at the expense of the switching loss of the high side MOSFET.

#### **Controller Layout**

The PCB layout of analog signal, feedback signal and current limiting circuit of the whole step-down module LGS51215 should be considered very carefully:

- A ground plane is generally required to separate the power level from the signal layer to provide good noise shielding.

- All sensitive analog signals and components (such as COMP,FB, CSN, CSP) should be kept away from high voltage switching nodes (SW, GH, GL, BST) to avoid coupling.

- The feedback resistor R8 can be directly connected to the output voltage VOUT detection point or to the output large capacitor.

- Differential detection of CSN and CSP needs to be side by side on the same PCB layer or overlapping on adjacent layers. The OCP setup resistor R9 is connected between the CSP and VOUT. Ensure that the resistor is as close to the LGS51215 controller as possible to avoid coupling of the connection loop from CSP to R9 with the high voltage node.

- The current loop of VCC, VCCP and VIN to GND through their respective decoupling capacitors is minimized, even if these decoupling capacitors are placed as close to the IC as possible.

#### **Thermal Layout**

For a switching power supply controller like LGS51215, the operating temperature range is influenced by many factors, such as the average gate drive current of a power MOSFET, switching frequency, input voltage, package characteristics, and operating environment.

In order for LGS51215 to work stably within the specified temperature range, the package must be able to dissipate heat effectively while keeping the junction temperature within the rated range. LGS51215 uses a 3mm x 3mm QFN-20L package that provides a heat dissipation PAD at the bottom to effectively remove heat in the package. The PCB design should be equipped with heat shield, heat dissipation through hole, and grounding plane to assist the heat dissipation PAD to complete heat dissipation.

Rev.A V1.0 July,2022

The drain of the high MOSFET is connected to the VIN plane for heat dissipation, while the drain of the low MOSFET is connected to the SW plane, but the SW area is deliberately designed to be relatively small compared to the VIN plane to alleviate electromagnetic interference problems.

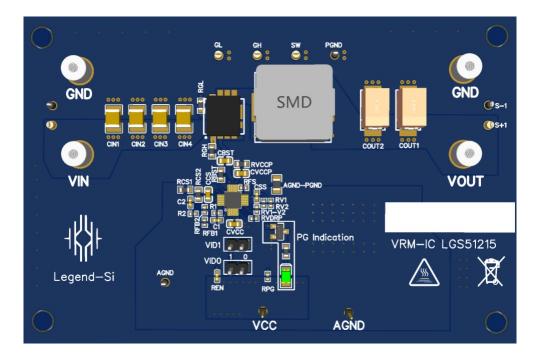

# **PCB Layout Reference**

Figure 14.1 provides a reference PCB layout for LGS51215 applications. For more information about recommended application solutions, refer to the LGS51215 EVM Board user manual.

Figure 14.1 PCB Layout Reference

# **Description Of Package**

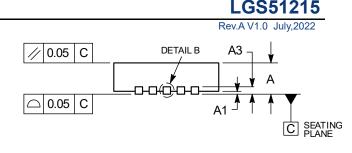

#### BOTTOM VIEW

# SOLDERING FOOTPRINT

SIDE VIEW

| DIM | MILLIMETERS |      |  |

|-----|-------------|------|--|

|     | MIN         | MAX  |  |

| А   | 0.80        | 1.00 |  |

| A1  |             | 0.05 |  |

| A3  | 0.20 REF    |      |  |

| b   | 0.15        | 0.25 |  |

| D   | 3.00 BSC    |      |  |

| D2  | 1.60        | 1.80 |  |

| Е   | 3.00 BSC    |      |  |

| E2  | 1.60        | 1.80 |  |

| е   | 0.40 BSC    |      |  |

| K   | 0.20 REF    |      |  |

| L   | 0.20        | 0.40 |  |

#### NOTE:

- All linear dimensions are in millimeters. Any dimensions in parentheses are for reference only. Dimensioning and tolerancing per ASME Y14.5M

- (2) This drawing is subject to change without notice.

- (3) This dimension does not include the burrs of the moulds. The burrs or protrusions on each side of the moulds shall not exceed 0.25 mm.

# IMPORTANT NOTICE AND DISCLAIMER

and Legend- si are trademarks of Legend- Si Semiconductor Co., Ltd. Legend- si holds a number of patents, trademarks, trade secrets and other intellectual property rights. Legend-Si provides technical and reliability data (including datasheets), design resources (including reference designs), applications or other design recommendations, networking tools, safety information and other resources "as is". No warranty is made that it is free from any defect, and no warranty, express or implied, is made, including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

The resources are available for professional developers to design with the Legend-Si product. You are solely responsible for: (1) selecting the appropriate Legend-Si product for your application; (2) Design, validate and test your application; (3) Ensure that your application meets relevant standards and any other safety, security or other requirements. Resources are subject to change without notice. Legend- Si's license for your use of the Resources is limited to applications related to the Legend- Si products involved in the development of the resources. Otherwise, no copying or display of the resources is permitted, and no other Legend- Si or any third-party intellectual property licenses are provided. Legend- Si will not be liable for any claims, damages, costs, losses or liabilities arising out of the use of the Resources and you shall indemnify Legend- SI and its representatives for damages arising therefrom. The Products provided by Legend- Si are subject to the Terms of Sale of Legend- Si and other applicable terms provided by Legend- Si Products on or with www.Legend-si.com. The provision of the resources by Legend- Si does not extend or otherwise change the applicable warranty coverage or warranty disclaimer issued by Legend- Si with respect to the Legend- Si Products.

Mailing address: Rm 1403, Tengfei Suite C Bldg., No.88 jiangmiao Rd., Pukou Dist., Nanjing, Jiangsu Prov. Telephone: 025-58196091